| Technology

Domain expertise is key to success for next generation cutting edge products. Aaroh Labs has extensive experience in SoCs targeted to technology areas like Storage, Networking, IoT and Analog. At Aaroh Labs we believe that development flows and methodologies play very important role in deciding quality and reliability of the design and predictability of the execution. We understand the importance of Domain expertise and adopting best design practices while designing future ready products.

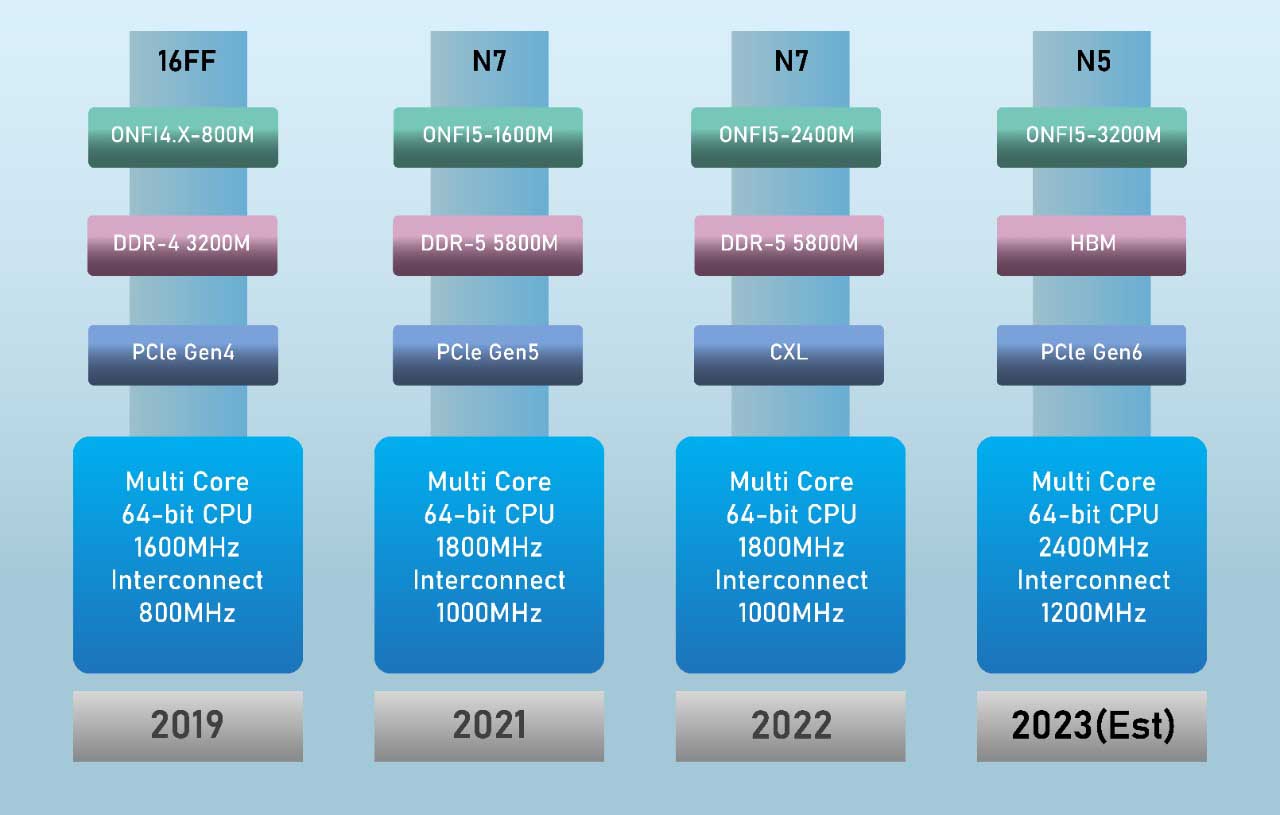

| Nodes progression

Aaroh Labs has transitioned from 16nm FF to 7nm till 2022. The design involves multi core 64bit CPUs, PCIe Gen4/5, ONFi4/5. Proposed design expected to start early 2023 has CXL and HBM.

| Flows and Methodologies

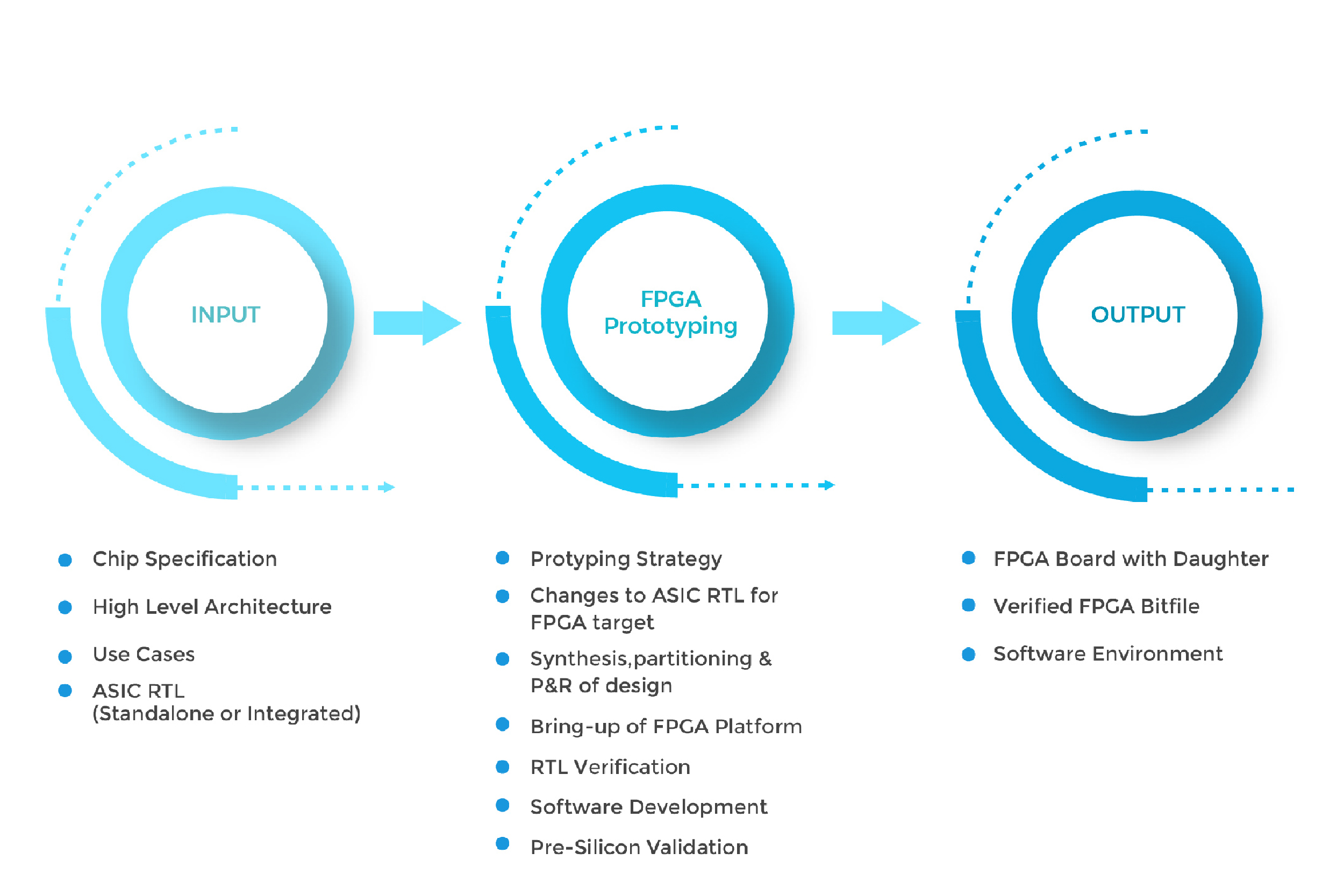

■ Front End Flow Methodology

■ Pre-Silicon Validation Methodology

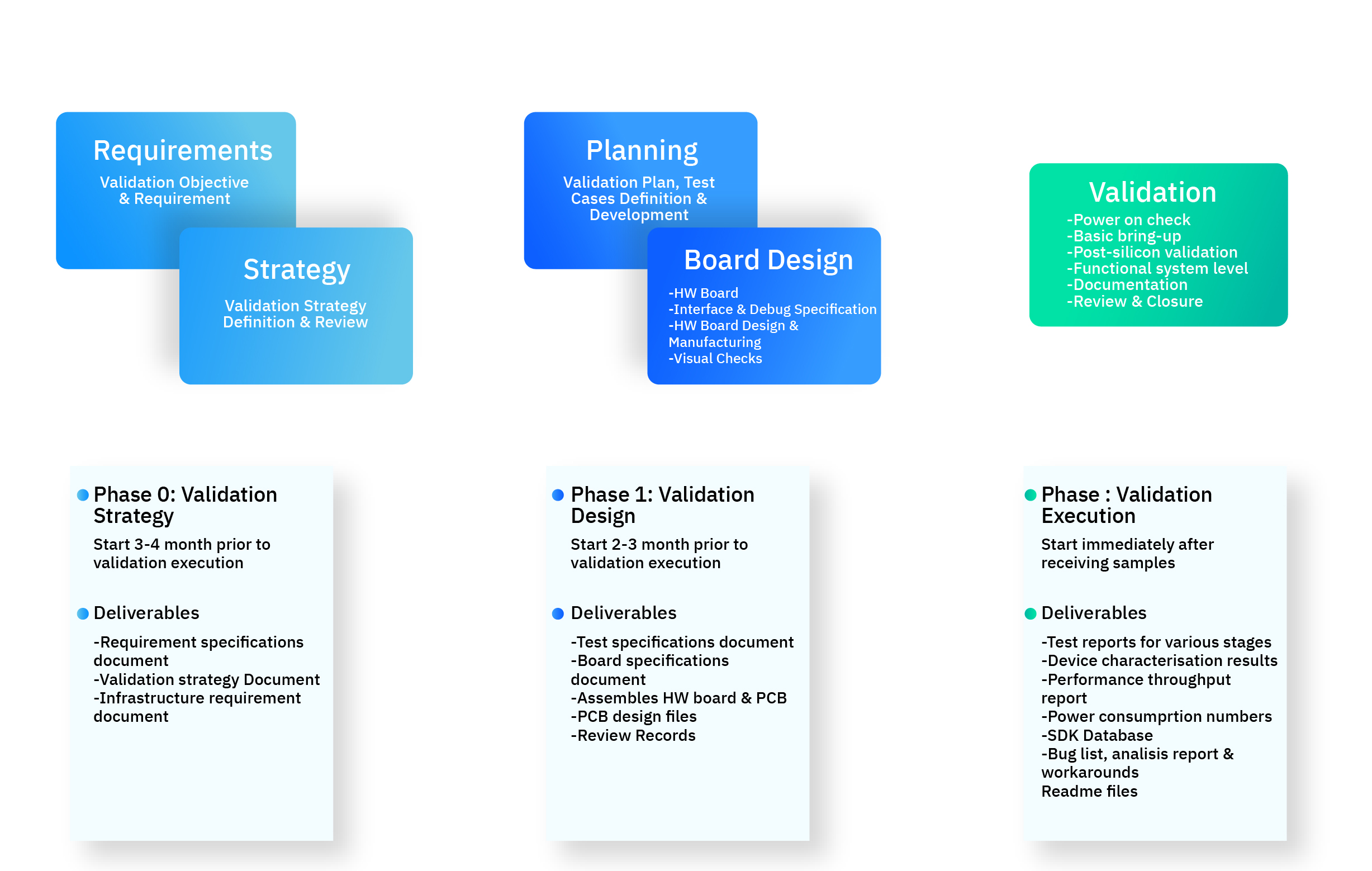

■ Post-Silicon Validation Methodology

| IP

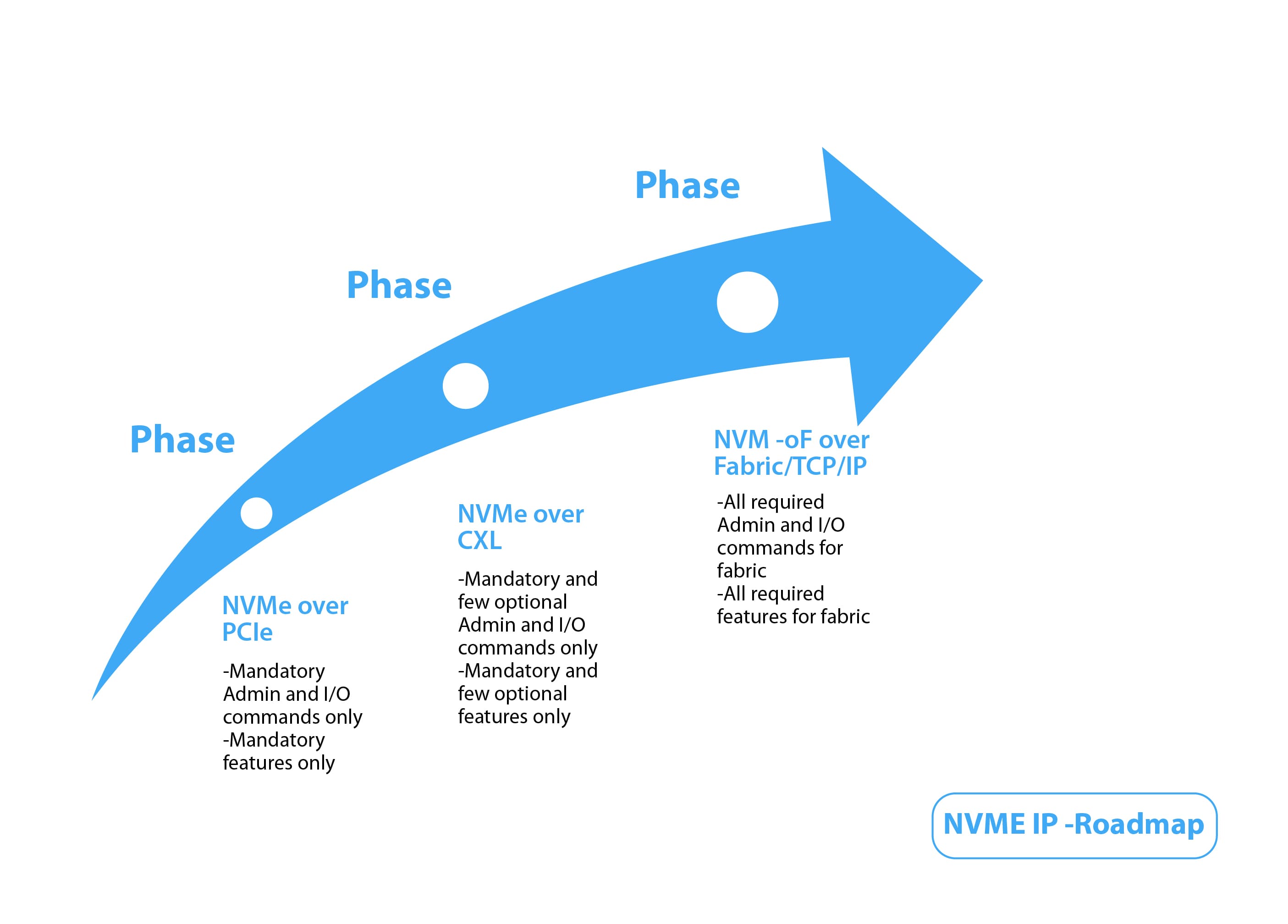

■ NVME IP

NVMe is a storage interface specification for Solid State Drives (SSDs) on the PCI Express (PCIe) bus. As NVMe devices have been widely used in a broad spectrum of computing domains, storage vendors have been using their own intellectual property (IP) cores to build high speed NVMe controllers. The NVMe specification stipulates that the NVMe controller IP cores be implemented in either firmware or hardware. Many storage vendors and communities typically implement the controller IP cores as firmware. Even though firmware-based controllers are sufficient to manage flash, the firmware execution can be a critical performance bottleneck when used in conjunction with faster NVM media.

Proposed Phase1 IP features

- NVM Express 2.0 specification mandatory features supported

- NVM Express 2.0 specification mandatory Admin and I/O commands supported

- Implements the registers specified in NVM Express 2.0 specification

- Manages the Submission Queue/Completion Queue doorbells from the host

- SQ arbitration

- PRP support